二维半导体材料在超越硅基晶体管极限的逻辑器件缩放上具有巨大潜力。然而,目前缺少被广泛接受的比较两种技术的方式。因此,需要建立适当的标准来对比二维晶体管和硅基晶体管,为二维晶体管的未来发展提供指引。

近日,12bet手机端app官网吴朋研究员、彭练矛院士应邀对建立二维晶体管与硅基晶体管基准测试标准进行评述,相关成果以题为“Setting a standard for benchmarking 2D transistors with silicon”的评论文章,于9月12日在线发表于电子学顶级期刊《Nature Reviews Electrical Engineering》。12bet手机端app官网吴朋研究员为第一作者,12bet手机端app官网毕业生、麻省理工学院博士后姜建峰博士为第二作者,彭练矛院士为通讯作者。

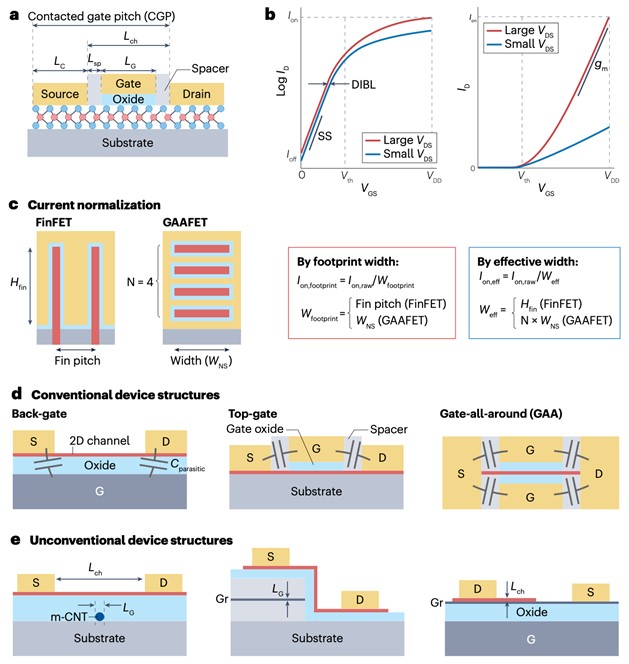

文章提出,随着二维晶体管的发展和成熟,其与商用硅基器件的直接比较是走向产业化的先决条件。逻辑器件基准测试的主要标准为性能(Performance),功耗(Power)和面积(Area),应在这三个方面对二维晶体管进行协同优化和基准测试。在性能方面,推荐使用本征门延迟τ和开态电流ION作为基准指标,并且应在给定供电电压VDD和关态电流IOFF目标的前提下比较ION,为了公平比较不同器件结构,建议使用有效宽度Weff(图1c)进行电流归一化;在功耗方面,降低VDD和寄生电容(图1d)对降低功耗至关重要,推荐使用给定ION、IOFF目标下的VDD,以及能量延迟积(EDP)作为基准指标;在面积方面,栅极长度LG和沟道长度Lch是重要指标,也应同时考虑接触和侧墙的尺寸,推荐使用接触栅极间距(CGP,图1a)作为基准指标,而对于非传统器件结构(图1e),应比较器件在芯片上实际占据面积。

文章截图

图1. 二维晶体管与硅基晶体管基准测试

这项工作为二维晶体管与硅基晶体管的对比提供了一个全面的基准测试框架,涵盖了性能、功耗和面积等关键方面,为未来二维晶体管技术的发展和产业化应用提供了重要指导。

原文链接:https://www.nature.com/articles/s44287-024-00093-y