未来集成电路对于性能×功耗×面积(PPA)综合性能的追求,使得先进硅基集成电路制造逐渐放缓了对于技术节点和物理尺寸的极限缩减,转而发展垂直维度晶体管与电路的三维集成技术以寻求突破。相较于具有成熟应用市场的先进三维封装,单片三维集成技术基于半导体前道有源晶体管与后道互联的制造工艺,拥有更高的层间互联密度和晶体管集成密度,理论上拥有电路综合性能的更高潜力。硅基单片三维集成领域的研究中,受制于晶体管热容限问题,上层单晶硅沟道与有源晶体管制备温度被迫降低,导致上层性能相较于硅基先进技术节点存在较大差距,仍然存在一定的瓶颈。高密度,高半导体纯度的平行阵列碳纳米管材料,拥有低温的材料制备与晶体管加工工艺,具备较高的热容限水平,有利于单片三维集成加工。并且,单片三维集成架构减少了碳管电路的互联长度,有利于电路速度的提升(Nano Res. 2019;12(8):1810)。因此,碳纳米管晶体管非常适合构建高速单片三维集成电路。但是,碳纳米管单片三维集成领域仍然缺乏高质量的层间工艺与上层沟道材料,限制了单片三维集成晶体管与电路的性能表现。

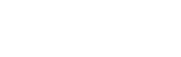

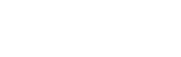

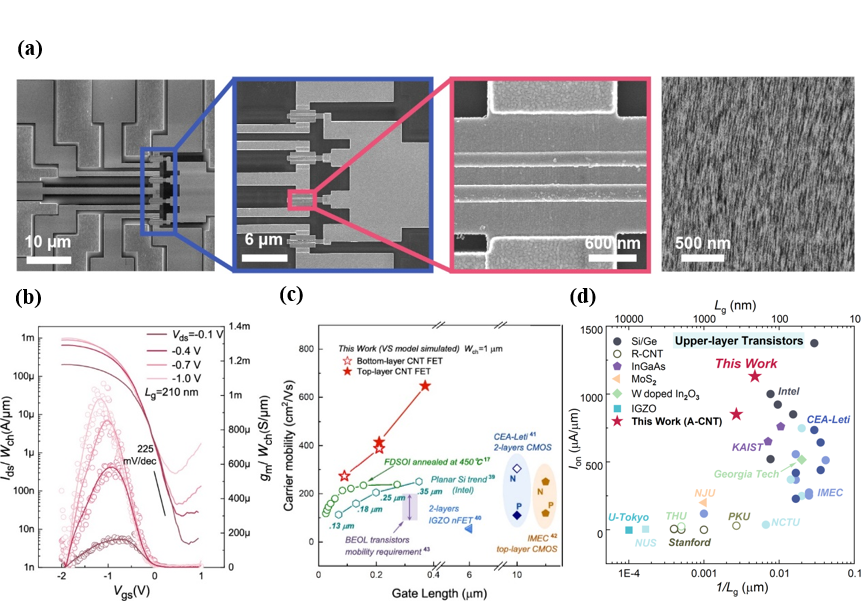

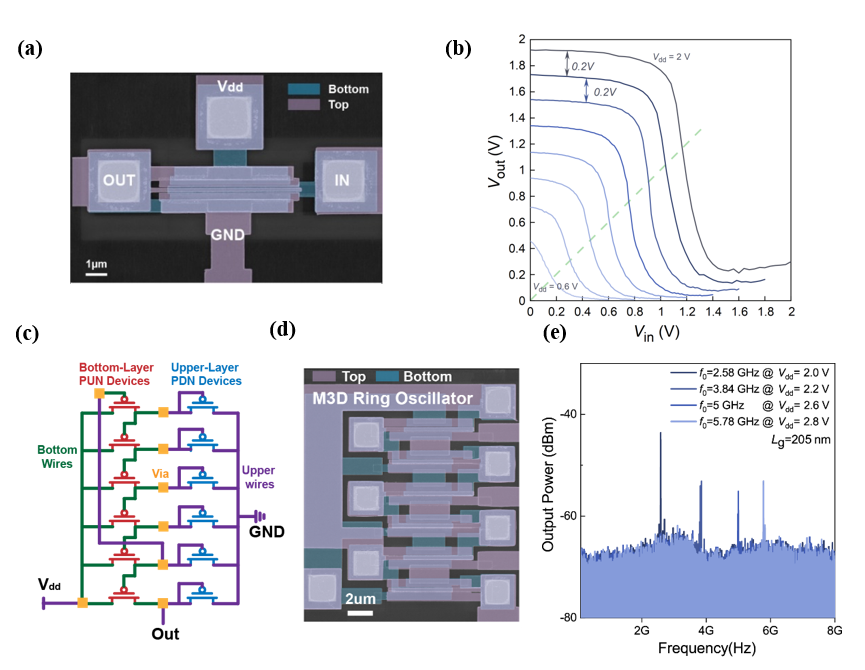

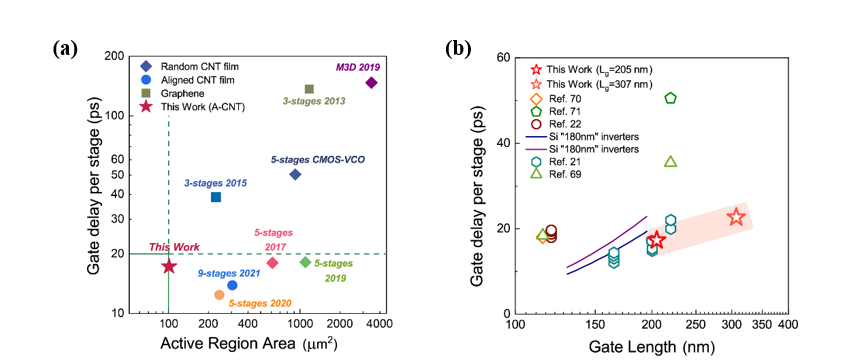

12bet手机端app官网、碳基电子学研究中心、纳米器件物理与化学教育部重点实验室张志勇教授课题组与浙江大学材料科学与工程学院金传洪教授课题组合作,对阵列碳纳米管单片三维集成关键工艺深入研究,利用具有自发平坦化的旋涂玻璃硅(SOG)材料,实现了高质量层间介质制备,具有高平坦度,低表面粗糙度(Ra<0.5 nm)与低介电常数(k~3),实现了碳管晶体管超细粒度的垂直集成,层间对准精度接近20 nm(图1a-d)。底层阵列碳管晶体管表现出超高的开态驱动性能,在90 nm栅长和-0.7 V漏端偏压下具有1.84 mA/μm的饱和电流与1.65 mS/μm的峰值跨导,超越了硅基45 nm节点PMOS晶体管跨导能力(图2a-c)。基于定向无损的低温转移工艺,团队在层间介质表面制备了高密度阵列碳纳米管,场效应迁移率高达650 cm2/Vs;通过满足底层晶体管稳定性的低温制备工艺,团队在上层构建了阵列碳管顶栅晶体管,开态电流密度超越硅基、有机半导体、二维材料等单片三维集成研究工作中上层晶体管的性能(图3.a-d)。团队进一步实现了电路层级的拓扑,制在100μm2面积内实现了单片三维集成的五阶环形振荡器电路,并最高取得5.78 GHz的输出振荡频率(图4a-d),对应17 ps的单级门延时,实现了纳米材料领域内速度最快、面积最小的三维集成电路(图5a-b)。

相关研究成果以题为“用于高性能集成电路的阵列碳管晶体管单片三维集成”(Monolithic three-dimensional integration of aligned carbon nanotube transistors for high-performance integrated circuits)的论文,于4月25日在线发表于《InfoMat》(https://doi.org/10.1002/inf2.12420)。2018级博士研究生樊晨炜为第一作者,张志勇教授为通讯作者。

上述研究得到国家重点研发计划、国家自然科学基金、北京市科委重大项目、季华实验室基金等项目的资助。

原文链接:https://doi.org/10.1002/inf2.12420

图1:高质量层间工艺与碳管晶体管单片三维集成

图2:底层碳管高性能碳管晶体管表征

图3:上层阵列碳管、晶体管性能表征与比较

图4:单片三维集成反相器与五阶环形振荡器表征

图5:单片三维集成环振电路速度×面积综合性能比较